In digital design, changing the sign of a number is a common operation, especially in arithmetic and signal processing applications. This blog post will walk you through implementing a sign changer module in Verilog. We’ll explore the functionality, the code, and how it leverages a few fundamental components like an 8-bit adder and a 2-to-1 multiplexer.

What is Sign Changer

The sign changer module takes an 8-bit input a and a control signal sign. Based on the value of the sign, it either outputs the original value of a or its two’s complement, effectively changing its sign.

The module also provides an overflow flag to indicate if the operation resulted in an overflow.

Verilog Code: Sign Changer

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 |

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// module SignChanger( input [7:0] a, input sign, output[7:0] b, output overflow ); wire [7:0] c; wire w; eightbitadder add (.A(~a), .B(8'b00000001), .Cin(8'b0), .S(c), .Cout(w)); twotoonemux mux (.i0(a), .i1(c), .s(sign), .out(b)); assign overflow = a[7] & ~(|a[6:0]) & sign; endmodule |

Code Explanation

- Module Declaration and Ports:

input [7:0] a: 8-bit input number.input sign: Control signal to determine if the sign should be changed.output [7:0] b: 8-bit output number with the potentially changed sign.output overflow: Output flag to indicate overflow.

- Internal Signals:

wire [7:0] c: Internal wire to store the result of the two’s complement operation.wire w: Internal wire to capture the carry-out from the adder.

- 8-bit Adder Instantiation:

- The

eightbitadderinstance computes the two’s complement ofaby adding1to the bitwise NOT ofa.

- The

- 2-to-1 Mux Instantiation:

- The

twotoonemuxinstance selects between the original inputaand its two’s complementcbased on thesigncontrol signal. Ifsignis0, the outputbisa; ifsignis1, the outputbisc.

- The

- Overflow Detection:

- The overflow logic checks if the input

ais the smallest negative number in 2’s complement form (10000000) and if thesigncontrol signal is set. If both conditions are true, it sets theoverflowflag.

- The overflow logic checks if the input

Verilog testbench code : Sign Changer

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 |

`timescale 1ns / 1ps module SignChanger_tb; reg [7:0] a; reg sign; wire [7:0] b; wire overflow; // Instantiate the SignChanger module SignChanger uut ( .a(a), .sign(sign), .b(b), .overflow(overflow) ); initial begin // Test case 1: Positive number, no sign change a = 8'd42; sign = 1'b0; #10; $display("a = %d, sign = %b, b = %d, overflow = %b", a, sign, b, overflow); // Test case 2: Positive number, sign change a = 8'd42; sign = 1'b1; #10; $display("a = %d, sign = %b, b = %d, overflow = %b", a, sign, b, overflow); // Test case 3: Negative number, no sign change a = 8'b11110110; // -10 in two's complement sign = 1'b0; #10; $display("a = %d, sign = %b, b = %d, overflow = %b", a, sign, b, overflow); // Test case 4: Negative number, sign change a = 8'b11110110; // -10 in two's complement sign = 1'b1; #10; $display("a = %d, sign = %b, b = %d, overflow = %b", a, sign, b, overflow); // Test case 5: Smallest negative number, sign change a = 8'b10000000; // -128 in two's complement sign = 1'b1; #10; $display("a = %d, sign = %b, b = %d, overflow = %b", a, sign, b, overflow); // End of test $finish; end endmodule |

Constraints file : Basys3 board

Modify this file when you are preparing for synthesis, implementation, and bitstream generation. Be sure to activate the necessary properties when using it. You can ignore this file for simulation purposes.

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143 144 145 146 147 148 149 150 151 152 153 154 155 156 157 158 159 160 161 162 163 164 165 166 167 168 169 170 171 172 173 174 175 176 177 178 179 180 181 182 183 184 185 186 187 188 189 190 191 192 193 194 195 196 197 198 199 200 201 202 203 204 205 206 207 208 209 210 211 212 213 214 215 216 217 218 219 220 221 222 223 224 225 226 227 228 229 230 231 232 233 234 235 236 237 238 239 240 241 242 243 244 245 246 247 248 249 250 251 252 253 254 255 256 257 258 259 260 261 262 263 264 265 266 267 268 269 270 271 272 273 274 275 276 277 278 279 280 281 282 283 284 285 286 287 288 289 290 291 292 293 294 295 296 297 298 299 300 301 |

## This file is a general .xdc for the Basys3 rev B board ## To use it in a project: ## - uncomment the lines corresponding to used pins ## - rename the used ports (in each line, after get_ports) according to the top level signal names in the project ## Clock signal set_property PACKAGE_PIN W5 [get_ports clkin] set_property IOSTANDARD LVCMOS33 [get_ports clkin] create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports clkin] ## Switches set_property PACKAGE_PIN V17 [get_ports {sw[0]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[0]}] set_property PACKAGE_PIN V16 [get_ports {sw[1]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[1]}] set_property PACKAGE_PIN W16 [get_ports {sw[2]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[2]}] set_property PACKAGE_PIN W17 [get_ports {sw[3]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[3]}] set_property PACKAGE_PIN W15 [get_ports {sw[4]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[4]}] set_property PACKAGE_PIN V15 [get_ports {sw[5]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[5]}] set_property PACKAGE_PIN W14 [get_ports {sw[6]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[6]}] set_property PACKAGE_PIN W13 [get_ports {sw[7]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[7]}] set_property PACKAGE_PIN V2 [get_ports {sw[8]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[8]}] set_property PACKAGE_PIN T3 [get_ports {sw[9]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[9]}] set_property PACKAGE_PIN T2 [get_ports {sw[10]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[10]}] set_property PACKAGE_PIN R3 [get_ports {sw[11]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[11]}] set_property PACKAGE_PIN W2 [get_ports {sw[12]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[12]}] set_property PACKAGE_PIN U1 [get_ports {sw[13]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[13]}] set_property PACKAGE_PIN T1 [get_ports {sw[14]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[14]}] set_property PACKAGE_PIN R2 [get_ports {sw[15]}] set_property IOSTANDARD LVCMOS33 [get_ports {sw[15]}] ## LEDs set_property PACKAGE_PIN U16 [get_ports {led[0]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}] set_property PACKAGE_PIN E19 [get_ports {led[1]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}] set_property PACKAGE_PIN U19 [get_ports {led[2]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[2]}] set_property PACKAGE_PIN V19 [get_ports {led[3]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[3]}] set_property PACKAGE_PIN W18 [get_ports {led[4]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[4]}] set_property PACKAGE_PIN U15 [get_ports {led[5]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[5]}] set_property PACKAGE_PIN U14 [get_ports {led[6]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[6]}] set_property PACKAGE_PIN V14 [get_ports {led[7]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[7]}] set_property PACKAGE_PIN V13 [get_ports {led[8]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[8]}] set_property PACKAGE_PIN V3 [get_ports {led[9]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[9]}] set_property PACKAGE_PIN W3 [get_ports {led[10]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[10]}] set_property PACKAGE_PIN U3 [get_ports {led[11]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[11]}] set_property PACKAGE_PIN P3 [get_ports {led[12]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[12]}] set_property PACKAGE_PIN N3 [get_ports {led[13]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[13]}] set_property PACKAGE_PIN P1 [get_ports {led[14]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[14]}] set_property PACKAGE_PIN L1 [get_ports {led[15]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[15]}] ##7 segment display set_property PACKAGE_PIN W7 [get_ports {seg[0]}] set_property IOSTANDARD LVCMOS33 [get_ports {seg[0]}] set_property PACKAGE_PIN W6 [get_ports {seg[1]}] set_property IOSTANDARD LVCMOS33 [get_ports {seg[1]}] set_property PACKAGE_PIN U8 [get_ports {seg[2]}] set_property IOSTANDARD LVCMOS33 [get_ports {seg[2]}] set_property PACKAGE_PIN V8 [get_ports {seg[3]}] set_property IOSTANDARD LVCMOS33 [get_ports {seg[3]}] set_property PACKAGE_PIN U5 [get_ports {seg[4]}] set_property IOSTANDARD LVCMOS33 [get_ports {seg[4]}] set_property PACKAGE_PIN V5 [get_ports {seg[5]}] set_property IOSTANDARD LVCMOS33 [get_ports {seg[5]}] set_property PACKAGE_PIN U7 [get_ports {seg[6]}] set_property IOSTANDARD LVCMOS33 [get_ports {seg[6]}] set_property PACKAGE_PIN V7 [get_ports dp] set_property IOSTANDARD LVCMOS33 [get_ports dp] set_property PACKAGE_PIN U2 [get_ports {an[0]}] set_property IOSTANDARD LVCMOS33 [get_ports {an[0]}] set_property PACKAGE_PIN U4 [get_ports {an[1]}] set_property IOSTANDARD LVCMOS33 [get_ports {an[1]}] set_property PACKAGE_PIN V4 [get_ports {an[2]}] set_property IOSTANDARD LVCMOS33 [get_ports {an[2]}] set_property PACKAGE_PIN W4 [get_ports {an[3]}] set_property IOSTANDARD LVCMOS33 [get_ports {an[3]}] ##Buttons set_property PACKAGE_PIN U18 [get_ports btnC] set_property IOSTANDARD LVCMOS33 [get_ports btnC] #set_property PACKAGE_PIN T18 [get_ports btnU] #set_property IOSTANDARD LVCMOS33 [get_ports btnU] #set_property PACKAGE_PIN W19 [get_ports btnL] #set_property IOSTANDARD LVCMOS33 [get_ports btnL] set_property PACKAGE_PIN T17 [get_ports btnR] set_property IOSTANDARD LVCMOS33 [get_ports btnR] #set_property PACKAGE_PIN U17 [get_ports btnD] #set_property IOSTANDARD LVCMOS33 [get_ports btnD] ##Pmod Header JA ##Sch name = JA1 #set_property PACKAGE_PIN J1 [get_ports {JA[0]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JA[0]}] ##Sch name = JA2 #set_property PACKAGE_PIN L2 [get_ports {JA[1]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JA[1]}] ##Sch name = JA3 #set_property PACKAGE_PIN J2 [get_ports {JA[2]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JA[2]}] ##Sch name = JA4 #set_property PACKAGE_PIN G2 [get_ports {JA[3]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JA[3]}] ##Sch name = JA7 #set_property PACKAGE_PIN H1 [get_ports {JA[4]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JA[4]}] ##Sch name = JA8 #set_property PACKAGE_PIN K2 [get_ports {JA[5]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JA[5]}] ##Sch name = JA9 #set_property PACKAGE_PIN H2 [get_ports {JA[6]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JA[6]}] ##Sch name = JA10 #set_property PACKAGE_PIN G3 [get_ports {JA[7]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JA[7]}] ##Pmod Header JB ##Sch name = JB1 #set_property PACKAGE_PIN A14 [get_ports {JB[0]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JB[0]}] ##Sch name = JB2 #set_property PACKAGE_PIN A16 [get_ports {JB[1]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JB[1]}] ##Sch name = JB3 #set_property PACKAGE_PIN B15 [get_ports {JB[2]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JB[2]}] ##Sch name = JB4 #set_property PACKAGE_PIN B16 [get_ports {JB[3]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JB[3]}] ##Sch name = JB7 #set_property PACKAGE_PIN A15 [get_ports {JB[4]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JB[4]}] ##Sch name = JB8 #set_property PACKAGE_PIN A17 [get_ports {JB[5]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JB[5]}] ##Sch name = JB9 #set_property PACKAGE_PIN C15 [get_ports {JB[6]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JB[6]}] ##Sch name = JB10 #set_property PACKAGE_PIN C16 [get_ports {JB[7]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JB[7]}] ##Pmod Header JC ##Sch name = JC1 #set_property PACKAGE_PIN K17 [get_ports {JC[0]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JC[0]}] ##Sch name = JC2 #set_property PACKAGE_PIN M18 [get_ports {JC[1]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JC[1]}] ##Sch name = JC3 #set_property PACKAGE_PIN N17 [get_ports {JC[2]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JC[2]}] ##Sch name = JC4 #set_property PACKAGE_PIN P18 [get_ports {JC[3]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JC[3]}] ##Sch name = JC7 #set_property PACKAGE_PIN L17 [get_ports {JC[4]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JC[4]}] ##Sch name = JC8 #set_property PACKAGE_PIN M19 [get_ports {JC[5]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JC[5]}] ##Sch name = JC9 #set_property PACKAGE_PIN P17 [get_ports {JC[6]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JC[6]}] ##Sch name = JC10 #set_property PACKAGE_PIN R18 [get_ports {JC[7]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JC[7]}] ##Pmod Header JXADC ##Sch name = XA1_P #set_property PACKAGE_PIN J3 [get_ports {JXADC[0]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JXADC[0]}] ##Sch name = XA2_P #set_property PACKAGE_PIN L3 [get_ports {JXADC[1]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JXADC[1]}] ##Sch name = XA3_P #set_property PACKAGE_PIN M2 [get_ports {JXADC[2]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JXADC[2]}] ##Sch name = XA4_P #set_property PACKAGE_PIN N2 [get_ports {JXADC[3]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JXADC[3]}] ##Sch name = XA1_N #set_property PACKAGE_PIN K3 [get_ports {JXADC[4]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JXADC[4]}] ##Sch name = XA2_N #set_property PACKAGE_PIN M3 [get_ports {JXADC[5]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JXADC[5]}] ##Sch name = XA3_N #set_property PACKAGE_PIN M1 [get_ports {JXADC[6]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JXADC[6]}] ##Sch name = XA4_N #set_property PACKAGE_PIN N1 [get_ports {JXADC[7]}] #set_property IOSTANDARD LVCMOS33 [get_ports {JXADC[7]}] ##VGA Connector #set_property PACKAGE_PIN G19 [get_ports {vgaRed[0]}] #set_property IOSTANDARD LVCMOS33 [get_ports {vgaRed[0]}] #set_property PACKAGE_PIN H19 [get_ports {vgaRed[1]}] #set_property IOSTANDARD LVCMOS33 [get_ports {vgaRed[1]}] #set_property PACKAGE_PIN J19 [get_ports {vgaRed[2]}] #set_property IOSTANDARD LVCMOS33 [get_ports {vgaRed[2]}] #set_property PACKAGE_PIN N19 [get_ports {vgaRed[3]}] #set_property IOSTANDARD LVCMOS33 [get_ports {vgaRed[3]}] #set_property PACKAGE_PIN N18 [get_ports {vgaBlue[0]}] #set_property IOSTANDARD LVCMOS33 [get_ports {vgaBlue[0]}] #set_property PACKAGE_PIN L18 [get_ports {vgaBlue[1]}] #set_property IOSTANDARD LVCMOS33 [get_ports {vgaBlue[1]}] #set_property PACKAGE_PIN K18 [get_ports {vgaBlue[2]}] #set_property IOSTANDARD LVCMOS33 [get_ports {vgaBlue[2]}] #set_property PACKAGE_PIN J18 [get_ports {vgaBlue[3]}] #set_property IOSTANDARD LVCMOS33 [get_ports {vgaBlue[3]}] #set_property PACKAGE_PIN J17 [get_ports {vgaGreen[0]}] #set_property IOSTANDARD LVCMOS33 [get_ports {vgaGreen[0]}] #set_property PACKAGE_PIN H17 [get_ports {vgaGreen[1]}] #set_property IOSTANDARD LVCMOS33 [get_ports {vgaGreen[1]}] #set_property PACKAGE_PIN G17 [get_ports {vgaGreen[2]}] #set_property IOSTANDARD LVCMOS33 [get_ports {vgaGreen[2]}] #set_property PACKAGE_PIN D17 [get_ports {vgaGreen[3]}] #set_property IOSTANDARD LVCMOS33 [get_ports {vgaGreen[3]}] #set_property PACKAGE_PIN P19 [get_ports Hsync] #set_property IOSTANDARD LVCMOS33 [get_ports Hsync] #set_property PACKAGE_PIN R19 [get_ports Vsync] #set_property IOSTANDARD LVCMOS33 [get_ports Vsync] ##USB-RS232 Interface #set_property PACKAGE_PIN B18 [get_ports RsRx] #set_property IOSTANDARD LVCMOS33 [get_ports RsRx] #set_property PACKAGE_PIN A18 [get_ports RsTx] #set_property IOSTANDARD LVCMOS33 [get_ports RsTx] ##USB HID (PS/2) #set_property PACKAGE_PIN C17 [get_ports PS2Clk] #set_property IOSTANDARD LVCMOS33 [get_ports PS2Clk] #set_property PULLUP true [get_ports PS2Clk] #set_property PACKAGE_PIN B17 [get_ports PS2Data] #set_property IOSTANDARD LVCMOS33 [get_ports PS2Data] #set_property PULLUP true [get_ports PS2Data] ##Quad SPI Flash ##Note that CCLK_0 cannot be placed in 7 series devices. You can access it using the ##STARTUPE2 primitive. #set_property PACKAGE_PIN D18 [get_ports {QspiDB[0]}] #set_property IOSTANDARD LVCMOS33 [get_ports {QspiDB[0]}] #set_property PACKAGE_PIN D19 [get_ports {QspiDB[1]}] #set_property IOSTANDARD LVCMOS33 [get_ports {QspiDB[1]}] #set_property PACKAGE_PIN G18 [get_ports {QspiDB[2]}] #set_property IOSTANDARD LVCMOS33 [get_ports {QspiDB[2]}] #set_property PACKAGE_PIN F18 [get_ports {QspiDB[3]}] #set_property IOSTANDARD LVCMOS33 [get_ports {QspiDB[3]}] #set_property PACKAGE_PIN K19 [get_ports QspiCSn] #set_property IOSTANDARD LVCMOS33 [get_ports QspiCSn] set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design] |

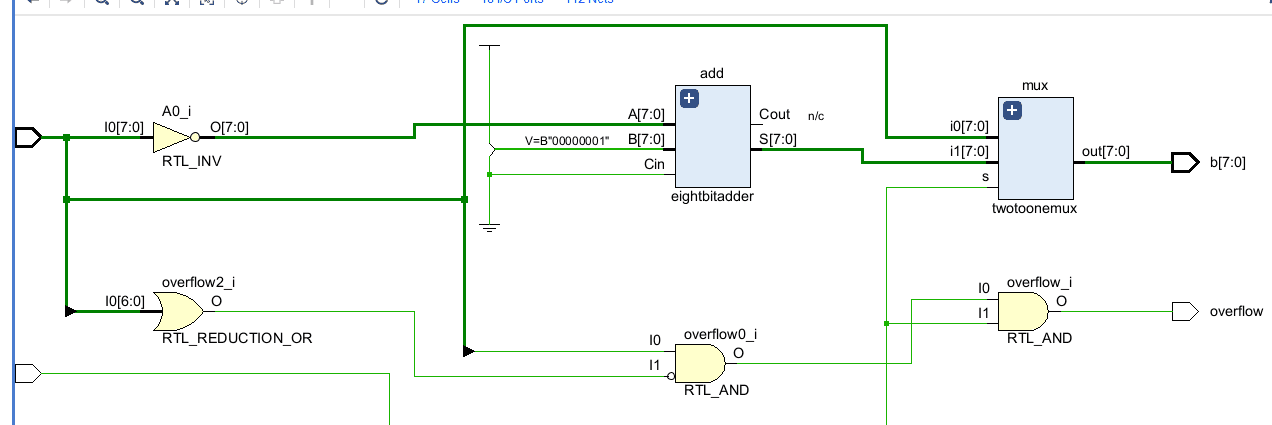

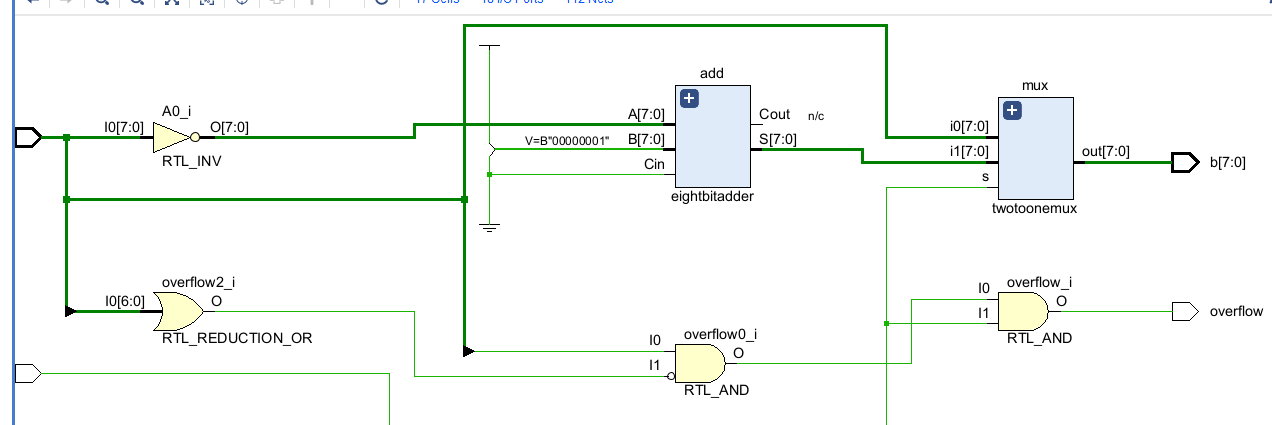

Schematic : SignChanger

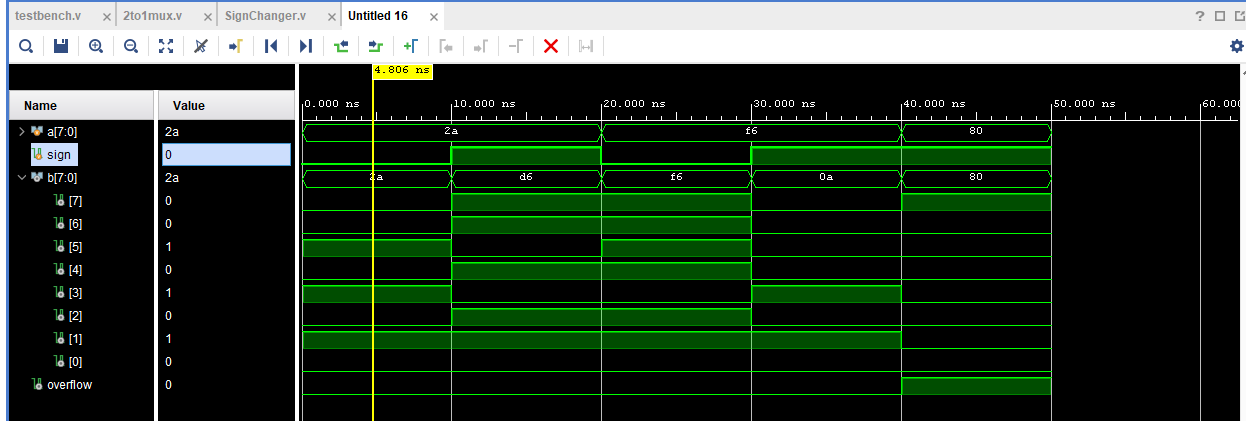

Simulation: Sign Changer

Conclusion

The SignChanger module is an essential tool in digital design for manipulating the sign of numbers. It leverages an 8-bit adder and a 2-to-1 multiplexer to efficiently perform this operation, providing flexibility and reliability in various applications.

Understanding and implementing such modules in Verilog equips you with the skills to handle more complex digital designs.

Stay tuned for more insightful articles on digital design and Verilog programming!

<—Prev

2×1 mux Verilog code

Next —->

hex to 7 segment decoder Verilog code